- 您现在的位置:买卖IC网 > Sheet目录1220 > IP-FIR (Altera)IP FIR COMPILER

�� �

�

�

�3–14�

�Chapter� 3:� Parameter� Settings�

�Specify� the� Architecture� Specification�

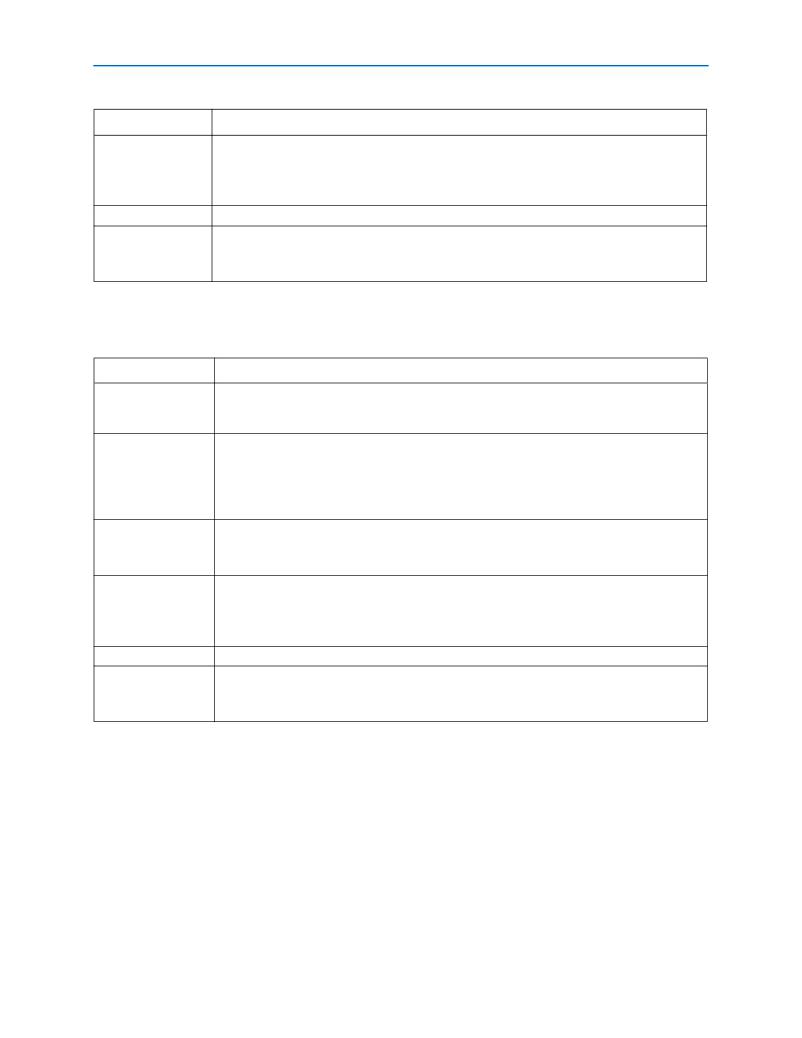

�Table� 3–6.� Multibit� Serial� Filter� Architecture� (Part� 2� of� 2)� (Note� 1)�

�Parameters�

�Coefficient� Reload�

�Pipeline� Level�

�Use� Single� Clock�

�Description�

�If� you� want� to� change� coefficients,� turn� on� this� option.� This� option� is� available� when� you� choose� to�

�store� coefficients� in� embedded� memory.�

�Selecting� this� option� increases� resource� usage,� turns� off� several� optimization� schemes,� and� adds�

�additional� input� ports� to� the� filter.�

�Creates� a� higher� performance� filter� with� a� resource� usage� increase.�

�Use� this� option� when� creating� designs� with� DSP� Builder.� This� option� is� only� available� when�

�Coefficients� Reload� is� selected� and� M512� ,� M4K� ,� MLAB� or� M9K� is� specified� in� Coefficient� Storage� .�

�This� option� ties� the� coef_clk_in� and� clk� signals� together.�

��(1)� The� bit� width� of� input� data� should� divide� evenly� by� the� number� of� serial� units� and� result� of� division� must� be� greater� than� or� equal� to� four.�

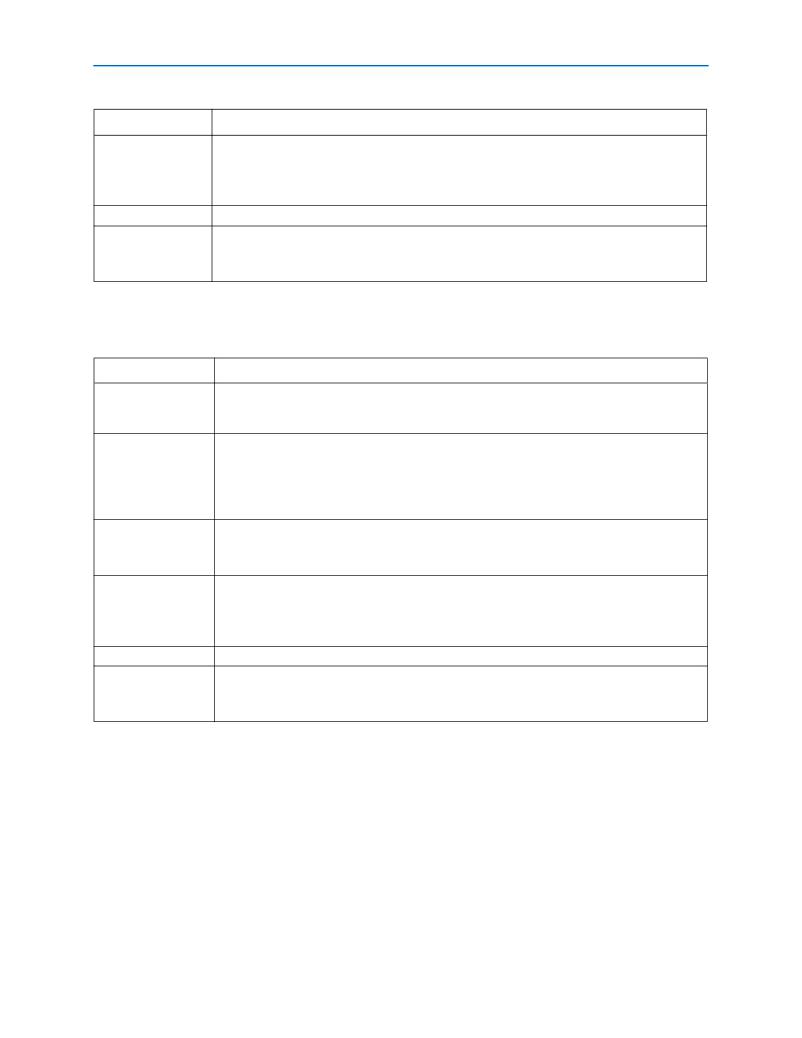

�Table� 3–7.� Fully� Parallel� Filter� Architecture�

�Parameters�

��Description�

�Data� Storage�

�Coefficient� Storage�

�Force� Non-Symmetric�

�Structure�

�Coefficient� Reload�

�Pipeline� Level�

�Use� Single� Clock�

�Specifies� the� device� resources� used� for� data� storage.� You� can� select� Logic� Cells� or� Auto� .� If� you�

�select� Auto� ,� the� Quartus� II� software� may� store� data� in� logic� cells� or� memory,� depending� on� the�

�resources� in� the� selected� device,� the� size� of� the� data� storage,� and� the� number� of� input� channels.�

�Specifies� the� device� resources� used� for� coefficient� storage.� You� can� select� Logic� Cells� ,� M512� ,�

�M4K� ,� MLAB� ,� M9K� ,� or� Auto� .� If� you� select� Auto� ,� the� Quartus� II� software� automatically� selects� the�

�most� appropriate� memory� block� size� for� the� selected� device.�

�The� option� list� changes� depending� on� which� device� you� select.� Selecting� embedded� memory�

�reduces� logic� cell� usage� and� may� increase� the� speed� of� the� filter.�

�If� you� want� to� create� a� design� that� uses� both� symmetric� and� non-symmetric� coefficients,� turn� on�

�this� option.� Non-symmetric� architectures� may� use� more� resources.�

�This� option� is� available� when� coefficients� are� stored� in� the� embedded� memory.�

�If� you� want� to� change� coefficients,� turn� on� this� option.� This� option� is� available� when� you� choose� to�

�store� coefficients� in� embedded� memory.�

�Selecting� this� option� increases� resource� usage,� turns� off� several� optimization� schemes,� and� adds�

�additional� input� ports� to� the� filter.�

�Creates� a� higher� performance� filter� with� a� resource� usage� increase.�

�Use� this� option� when� creating� designs� with� DSP� Builder.� This� option� is� only� available� when�

�Coefficients� Reload� is� selected� and� M512� ,� M4K� ,� MLAB� or� M9K� is� specified� in� Coefficient� Storage� .�

�This� option� ties� the� coef_clk_in� and� clk� signals� together.�

��(1)� When� input� data� is� unsigned,� the� input� data� bit� width� should� be� greater� than� or� equal� to� one.� When� input� data� is� signed,� the� input� data� bit� width�

�should� be� greater� than� or� equal� to� two.�

��?� May� 2011� Altera� Corporation�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

IP-NCO

IP NCO COMPILER

IP-NIOS

IP NIOS II MEGACORE

IP-PCI/MT64

IP PCI 64BIT MASTER/TARGET

IP-PCIE/8

IP PCI EXPRESS, X8

IP-POSPHY4

IP POS-PHY L4

IP-RIOPHY

IP RAPID I/O

IP-RLDRAMII

IP RLDRAM II CONTROLLER

IP-RSDEC

IP REED-SOLOMON DECODER

相关代理商/技术参数

IP-FIRII

功能描述:开发软件 FIR Compiler II MegaCore

RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors

IPFLBPT2

制造商:Carlo Gavazzi 功能描述:IL 35MM MUSH P-P PL 22MM RED

IPG1-0-90

制造商:Sensata Technologies 功能描述:1 Pole

IPG1-1-41-203-90

制造商:Sensata Technologies 功能描述:1 Pole

IPG1-1-51-103-A-00-V

制造商:Sensata Technologies 功能描述:Circuit Breaker Magnetic 1Pole 10A 65VDC

IPG1-1-52-303-A-00-V

制造商:Sensata Technologies 功能描述:Circuit Breaker Magnetic 1Pole 30A 65VDC

IPG1-1-61-153-00-V

制造商:Airpax 功能描述:Circuit Breaker Magnetic Circuit Protectors 1Pole 15A 制造商:Sensata Technologies 功能描述:Circuit Breaker Magnetic Circuit Protectors 1Pole 15A

IPG1-1-61-153-90-V

制造商:Airpax 功能描述:Circuit Breaker Magnetic Circuit Protectors 1Pole 15A 制造商:Sensata Technologies 功能描述:Circuit Breaker Magnetic Circuit Protectors 1Pole 15A